### **Features**

- Small, inexpensive bench-top unit

- Easy selection of test condition

- Logical input level definable

- Non-destructive and accurate tests can be repeated

- ESD Pulse source for trigger available (Optional)

- Vp pulse source for trigger available (optional)

- JEDEC over voltage method available (Optional)

- Optional IEEE 488 interface allows the automated Latch-up test system

## General Description

The Model 8600 is a manually operated latch-up tester. The trigger source of the latch-up can be selected from current pulse, voltage pulse, ESD pulse, programmable DC power supply, programmable over-voltage power supply or  $V_{DD}$  pulse. Test conditions are manually programmed via thumb-wheel switches and slide switches, or remotely programmed via IEEE 488 interface. Connections between a DUT and one of the trigger sources,  $V_{DD1}$  and  $V_{DD2}$  are made by the leads supplied as standard accessories.

Because the auxiliary power supply,  $V_{DD2}$  has also current measurement function, it can be used to measure  $I_{OH}$  or  $I_{OL}$  or as the latch-up trigger source for DC Latch-up test.

Each DUT pin can be connected to V<sub>DD</sub> or GND (Vss) through serial resistor or stays open by the slide switch on the DUT board. Switch box allows input pins at any desired logic levels so that sequential logic can be tested easily. Because the switch box includes level conversion capability, complicated digital patterns may be applied by connecting an external pattern generator or IC tester. ESD pulse triggered latch-up is allowed if ESD pulse generator options are specified. Model 8600 can be used in the fully automated latch-up test system by combining with a relay matrix and controlled by the host computer.

Power supply over-voltage test option superimposes the over-voltage pulse above the VDD and allows the test meeting the JEDEC standard. (Refer to the timing diagram next page) .

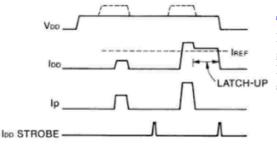

### Timing: Current Pulse (IP) method

IDD is measured at the specified strobe time, by gradually increasing amplitude of current pulse, I<sub>P</sub>. Latch-up is detected if I<sub>DD</sub>>I<sub>REF</sub>, then V<sub>DD</sub> supply is shut off right away.

Supply Over-voltage Test

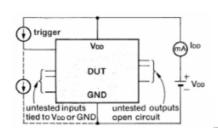

Current Pulse Latch-up Test

# **Standard Specifications**

**Current Pulse**

Output Floating

Amplitude ( $I_P$ ) 1 to 999mA/1mA Res. Width ( $t_P$ ) 0.1 to 99.9ms/0.1ms Res.

Clamp Voltage(V<sub>CLP</sub>) 5,7,10,20 or 50V

Strobe

$I_{DD}$  Strobe (t<sub>STB</sub>) -(t<sub>P</sub>-1ms) to (t<sub>OFF</sub>-1ms) V<sub>CLP</sub> Strobe At the end of t<sub>P</sub>

Programmable PS 1 (V<sub>DD1</sub>)

Output Floating

Voltage Range  $1\sim50\text{V}/0.1\text{V}$  Res. Current Range  $0\sim999\text{mA}/1\text{mA}$  Res.

Programmable PS 2 (V<sub>DD2</sub>)

Output Floating Voltage Range  $1\sim50\text{V}/0.1\text{V}$  Res. Current Range  $0\sim99.9\text{mA}/0.1\text{mA}$  Res.

Latch-up Reference Current (IREF) 5,10,20,50,100,200,300 or 500mA

Pin Count 64 pins (Built-in)

Test Mode Current Latch-up

\* Optional DC Latch-up

Pulse V<sub>DD</sub>Latch-up Supply Over-voltage\*

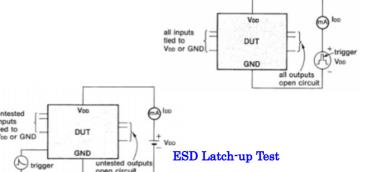

ESD Latch-up\*

AC Input AC100V, 50/60Hz

300VA

Size, Weight About 180H, 499W, 508D(m

m)

About 25kg

### **Options**

${\bf Simplified\ Pattern\ Generator: Opt.8601}$

Clock 6 channels

Data 8Channels

Amplitude Up to V<sub>DD1</sub>

VP Pulse Generator: Opt.8630

Used by Supply Over-voltage Test

ESD Pulse Generator: Opt.8602(HBM), Opt.8612(MM)

Max. Voltage: 1kV

ESD Pulse Generator: Opt.8620 (HBM, MM)

Current Limiter: Opt.8603

50, 200, 500, 1000mA

256 Pin Test Head: Opt.8615

64 pin DUT Board Kit: Opt.8608-1

256pin DUT Board Kit: Opt.8608-2

GP-IB Interface: Opt.8604

(Note)

Opt. 8601, 8603, 8604 should be ordered with the

main body.

(Specifications subject to change without notice.)

|             | (Specifications subject to change without notice.) |

|-------------|----------------------------------------------------|

| Contact to: |                                                    |

|             |                                                    |

|             |                                                    |

|             |                                                    |

|             |                                                    |

|             |                                                    |